主加法標準形

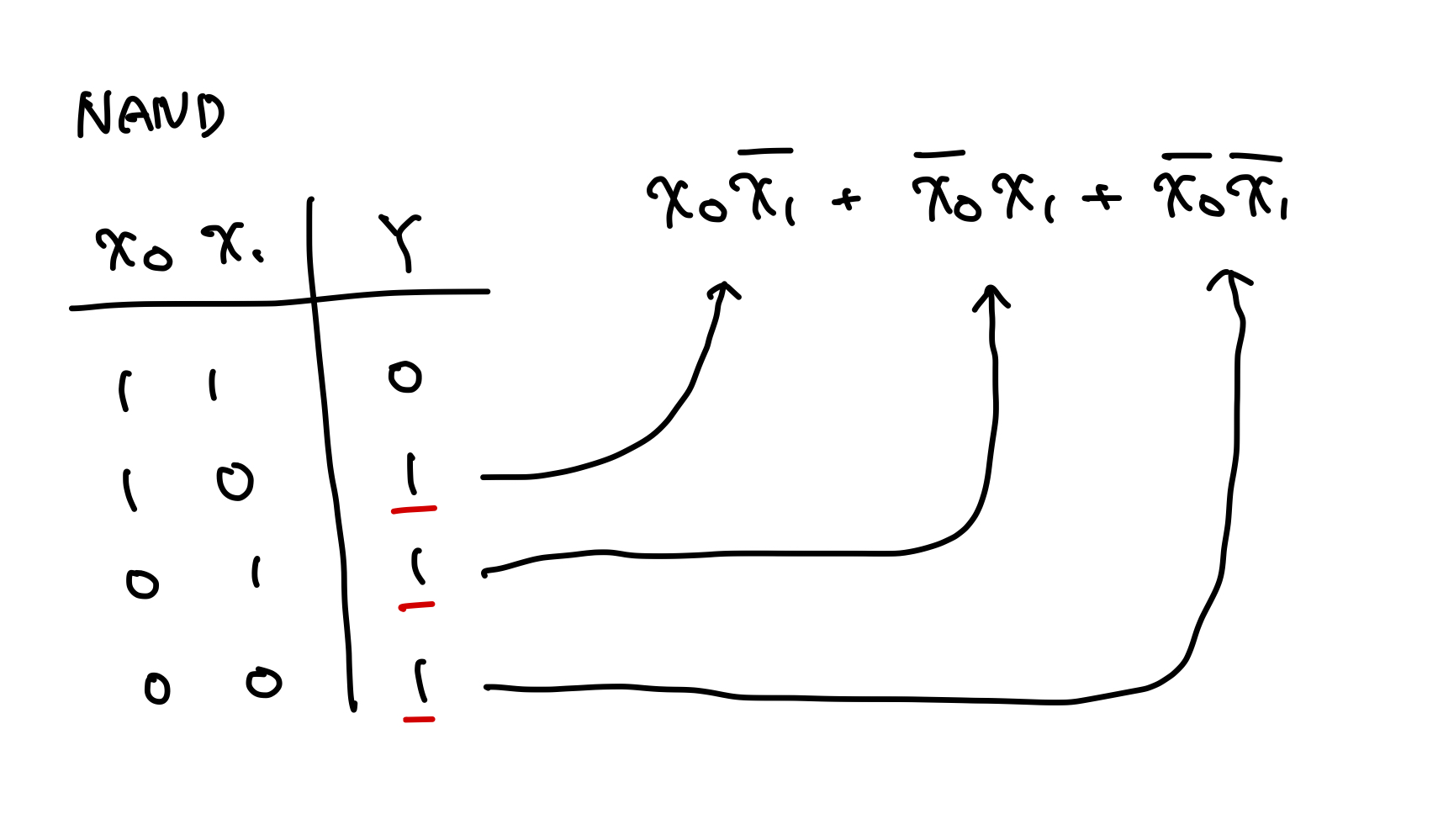

最小項同士の和の形になっている論理式。 真理値表から1を出力する入力変数の組み合わせから論理和を取ることで、簡単に欲しい出力を行う組み合わせ回路を構成することができる。これを加法標準形設計手法と呼ぶ。

NANDゲートを加法標準形設計手法で設計する

問題点

加法標準形設計手法で得られた組み合わせ回路は大きすぎる。 実際にNANDゲートはAND回路とNOT回路の2ゲートで構成できるが、上のように大量のゲートを必要とする。 したがって、論理式を簡約してから組み合わせ回路として実装する。

シノニム

- canonical Sum-of-Products (SOP)

- 論理和標準形

- 選言標準形

- Disjunctive normal form (DNF)